混合訊號晶片需求急遽升溫,預估未來數年內將超過數位訊號市場規模,然隨著混合訊號奈米製程迭有進展,設計成本將大幅攀升,使半導體業者挑戰加劇。尤其台積電於日前宣布擴展開放創新平台(OIP)服務,如系統級設計、類比/混合訊號/射頻設計與二維/三維(2D/3D)IC設計服務等,更加突顯混合訊號市場已成兵家必爭之地。

|

| Berkeley Design總裁暨執行長Ravi Subramanian表示,半導體廠商為確保出貨前的生產良率,晶片設計的成功比例將舉足輕重。 |

近期,與台積電針對混合訊號技術將有合作計畫的Berkeley Design總裁暨執行長Ravi Subramanian表示,半導體產業丕變,即便數位訊號晶片仍為最大宗市場,但混合訊號的前景相當可期,未來市場規模甚至將超過數位訊號,如高通(Qualcomm)、博通(Broadcom)、蘋果(Apple)、德州儀器(TI)、賽靈思(Xilinx)、明導國際(Mentor Graphics)等皆大張旗鼓進駐混合訊號市場。

另一方面,Subramanian強調,混合訊號奈米製程特定應用標準產品(ASSP)已勢不可當,未來90奈米、65奈米甚至45奈米以下製程將為高毛利市場,吸引眾多廠商搶進。相較於傳統SPICE裝置雜訊分析,奈米的SPICE精準度更高,且速度快五至二十倍,並具備分析超過一百萬件元件的能力。

根據市調機構iSuppli與可編程邏輯元件(PLD)廠商賽靈思資料顯示,隨著升級至更先進的製程,耗資最大的並非光罩和製造,反而是設計成本爆增,以45奈米為例,若總體成本為6,500萬美元,設計成本將高達4,000萬美元;至32奈米時,若總體成本為1億美元,設計成本甚至達到7,500萬美元。由此顯見,降低急速增長的設計成本將為晶片商面臨的重大課題。

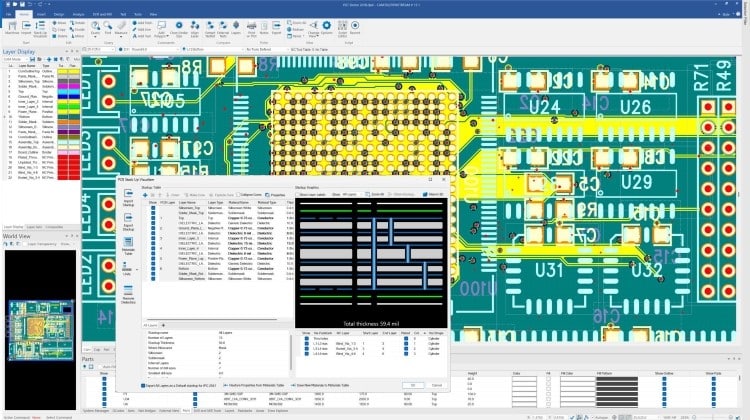

Subramanian認為,解決設計成本直線攀升之道為整合平台,其將透過改善的奈米實體層(PHY)、提高奈米SPICE的精準度、增加五至五十倍的速度及產能滿足市場需求。而為搶攻此一龐大商機,Berkeley Design正試圖藉由開發的設計自動化類比FastSPICE認證(AFS)平台支援無線通訊、消費性電子、運算、輸入/輸出(IO)、電源管理、記憶體、類比/混合訊號及射頻應用,目前已獲得全球共七十五家公司使用,其中包含前二十大中的十五家半導體廠商。

Berkeley Design成立於2003年,致力於提供類比、混合訊號及射頻整合積體電路分析工具開發,主要供應複雜類比、混合訊號及射頻半導體設計之快速量產的虛擬與分析軟體工具,其開發的AFS平台專注於高精準度、GHz認證設計的奈米晶片量產需求。